SIL Verification

Safety Integrity Level; or SIL Verification demonstrates the capability of a Safety Instrumented Function (SIF) in accordance with IEC 61508 and IEC 61511 against the following requirements:

– Quantifying the effect of random hardware failures (Probability of Failure on Demand (PFD) or the Average Frequency of Dangerous Failures (PFH));

– Hardware safety integrity architectural constraints (Safe Failure Fraction (SFF), Hardware Fault Tolerance (HFT), Element Type A or B);

– Systematic capability;

– Common Cause Failure (CCF).

Methods of SIL Verification

SIL Verification can be carried out using various modelling techniques including Reliability Block Diagrams (RBDs), Fault Tree Analysis (FTA) and Failure Mode and Effect Analysis (FMEA). Where the SIF fails to achieve the target failure measure or SIL, a sensitivity analysis can be carried out to demonstrate the effect of modifying certain factors. This includes the following factors:

– Maintenance strategy (repair time and proof test frequency);

– System architecture;

– Implementing diagnostic mechanisms;

– Minimising CCF.

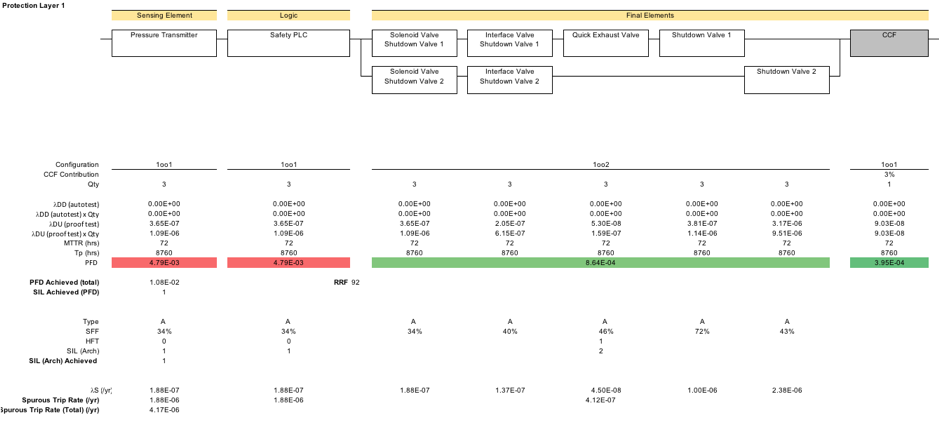

Example of an RBD

The following provides an example of a Reliability Block Diagram used for SIL Verification.

FAQ

As a minimum, the following information would be required in order to conduct the workshop:

– Existing SIL Determination report

– P&ID’s

– Cause and Effects Diagrams

– Interlock Lists and configurations

– Equipment Data Sheets and Reliability Data

ES will prepare a report describing the facility, the scope of work, a detailed methodology, the SIF’s being assessed along with their configurations and the data utilised, the results of the analysis (i.e. SIL achieved for each SIF), sensitivity analysis (if required) and any recommendations required.

Based on the results of the SIL Verification study, ES are also able to assist in writing detailed Safety Requirement Specifications (SRS) for each of the SIFs in accordance with the requirements of IEC 61508 and IEC 61511.

ES have worked with clients all over the world conducting SIL Verification studies. Through our consultants, we have verified over 1000 SIF loops against their target requirements. ES have managed to gather a vast amount of failure rate data for various devices, which are available to use at all times. For more information, or to discuss your needs for conducting a SIL Verification study, please contact us using the form below or email [email protected]